Dear team,

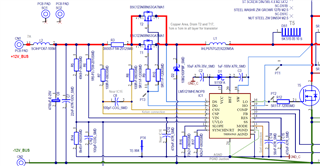

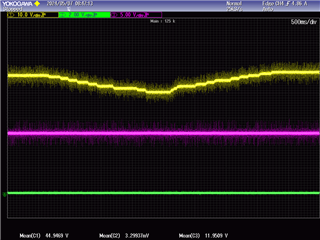

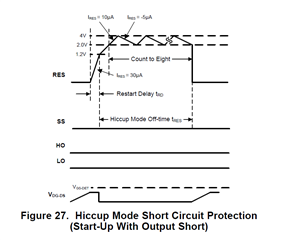

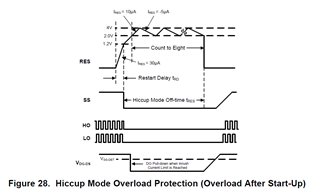

We have designed a boost inverter using "LM5121MHE". In case of having short circuit at the output I expect the NMOS T1 (As you see in the following photo) to open and shorten the input voltgae. But it seems that when there is a shortcircuit at the output, it just doesn't boost the voltage and I see the input voltage at the output. There is sth with this functionality (DG) that I don't understand. Can you take a look at the SCH and let me know if sth is wrong there?

Input: voltage 12V

Current 7A

Output: voltage 48V

Current 1.4A

Thanks in advanced

Farzaneh