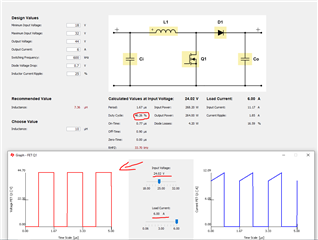

I have been tasked with testing someone else's design using the LM5156HPWPR chip and am having issues with delivering power at load. Smaller loads work as intended, but when I swap to the intended load it fails to deliver the output voltage and you can clearly hear clicking/switching coming from the board.

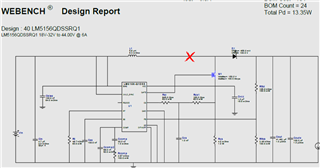

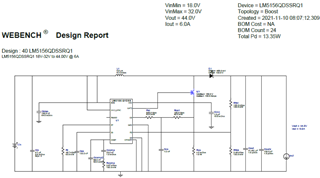

The designer seemed to very closely follow the design suggested by the WEBENCH tool, with the only significant differences I see being the addition of LED indicators.

I am fairly confident our supply is not the issue and while I have not gone over every trace I would broadly trust the designer's layout ability. I've familiarized myself with the chip and the datasheet and have not yet noticed any obvious errors. Any Input on the steps I could take isolating where the issue might be would be greatly appreciated!