Dear Team,

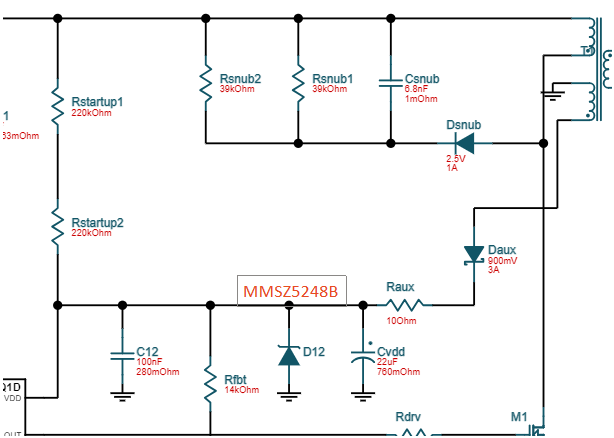

I am designing the flyback the with Vin 67 to 180rms, and Vo 12V, 2A. I have gone thru the Webench schematic, observed that 18V zener connected across VDD pin for protecting the IC.

the D12 is VZ 18V @ IZT 7mA, now the doubt is the since total RVDD are 440K, it allows 0.21mA at 67V rms. it should allow the 7mA+70uA to IC get start puls right ? how does 0.21mA helps ? Pls explain