Dear support team,

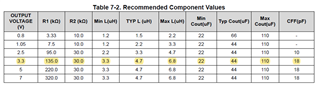

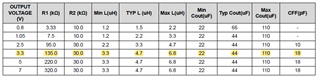

in the datasheet of the TPS562203, a max. output capacitance of 110uF is recommended:

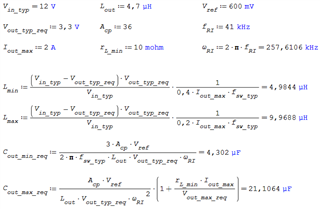

I cannot find any restrictions / calculations in the datasheet about the output capacitor.

In our application we are using a lot of decouling capacitors at the separate ICs which gets supplied from this power supply - in sum we have >100uF.

Do you see any problems, when driving a higher capacitance at the output? How can I determine the max. output capacitor?

Thank you for your support and kind regards,

Markus