hello,expert

I have checked the specification sheet of TPS92520 and have some questions about output open circuit fault case 3:

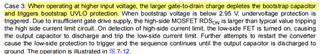

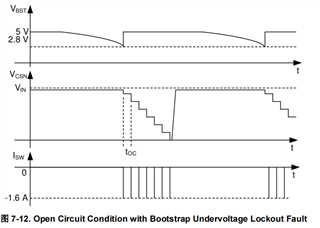

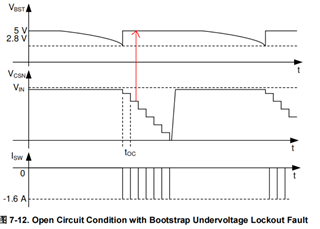

We can see the description in its datasheet,but i have some questions,please help explain in details.

1) When operating at higher input voltage, the larger gate-to-drain charge depletes the bootstrap capacitor and triggers bootstrap UVLO protection?what is the "larger gate-to-drain charge" ?

2) What caused the bootstrap capacitor undervoltage protection? Is it due to an open load?

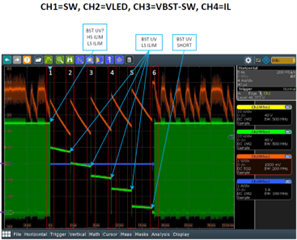

My understanding: First, the load is open → the chip operates in the minimum off time mode→Causing insufficient conduction time of LS MOS→bootstrap UVLO →HS LIMT→LS LIMT →repeat LS LIMT

Is my understanding above correct? Is the order correct?

3)When a low side MOS LIMT event occurs, will LS mos also immediately shut down?

4)What situations would trigger bootstrap UVLO protection if it were not for an open load condition?

5)if i apply the PWM DIMMING, Will bootstrap UVLO protection be triggered during PWM OFF time?

I have also seen other similar posts on the forum, but I did not understand them. Please help me explain them in detail again

thank you

best regards