Hi Team,

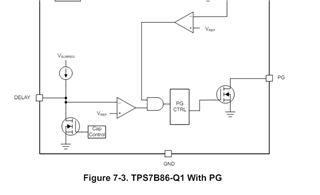

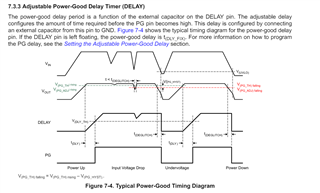

From the datasheet description, when the output is normal, the Delay will keep high, just like below picture shows:

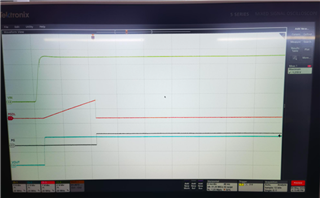

But when I use the EVM to have a test, I find the Delay pin will pull low when it meet the rise up threshold(1.2V), that is a expected behavior for you? Thank you.

Best Regards,

Kunyue