hello,

I use two ucc27712 to build a full H-Bridge.I tested the circuit today and i found some question.

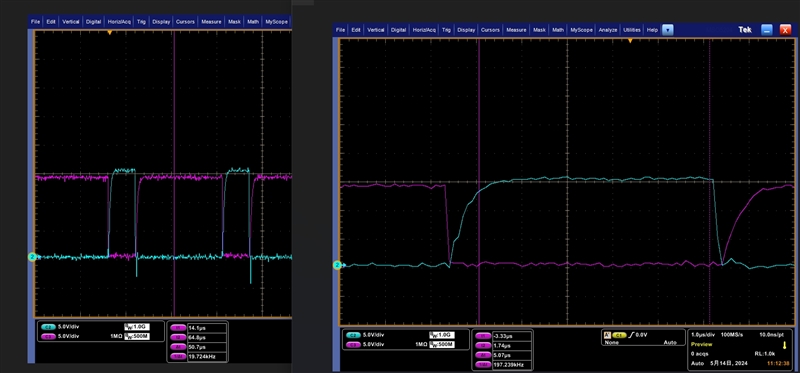

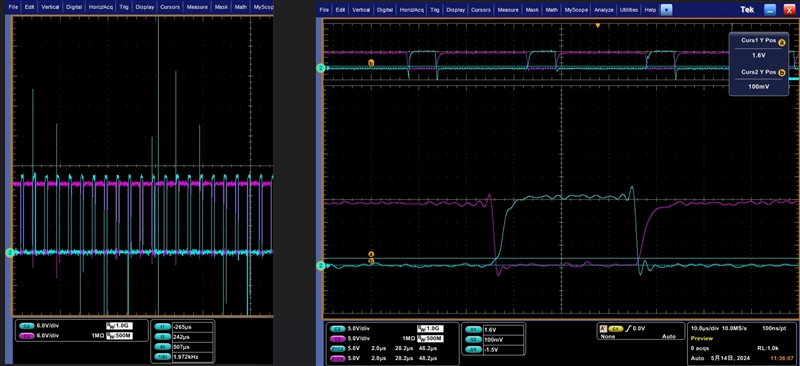

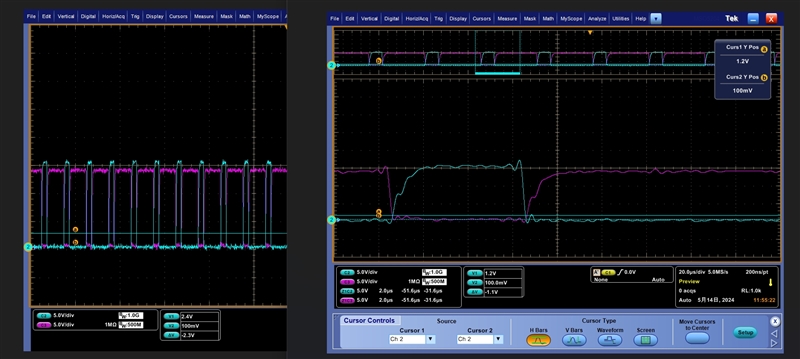

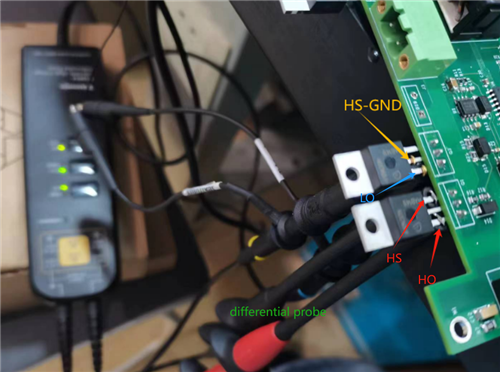

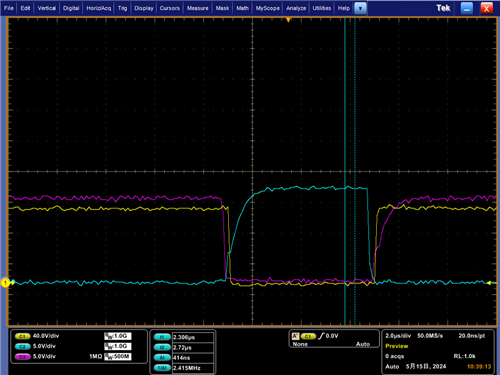

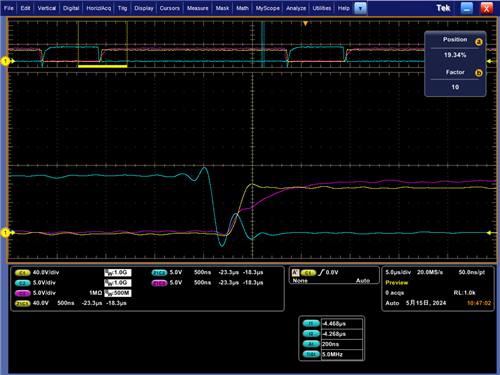

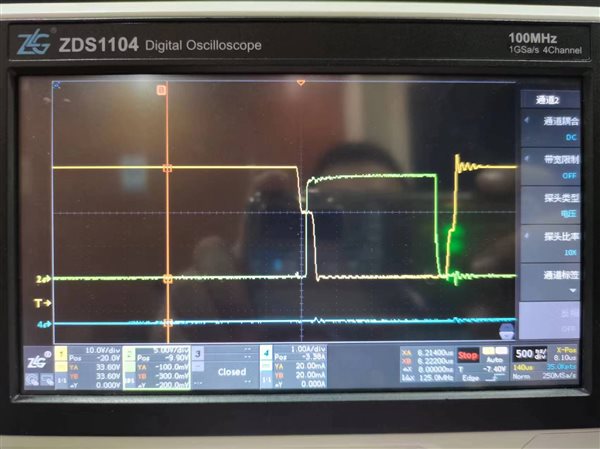

i first found the mosfet became hot when i diaconnected the load,and then i tested the output of the ucc27712,HO and LO waveform are as follow

i cannot understand the step during the falling of the output,and I think it is this reason that causes the upper and lower MOS to be turned on at the same time, causing them to heat up.

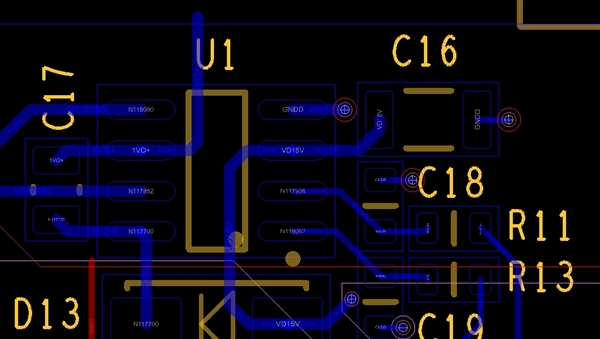

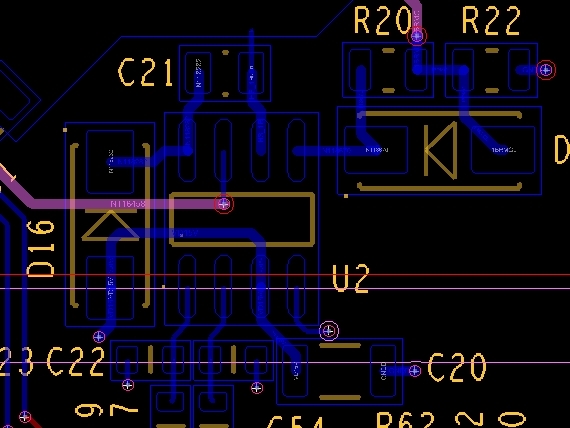

my schematic is as follow.part number of the mos is IPP410N30

i also tested the delay of the 74HC4049 and the value is about 8ns.

please help me