Other Parts Discussed in Thread: TPSI3052, , TPSI3052-Q1

Hello Team,

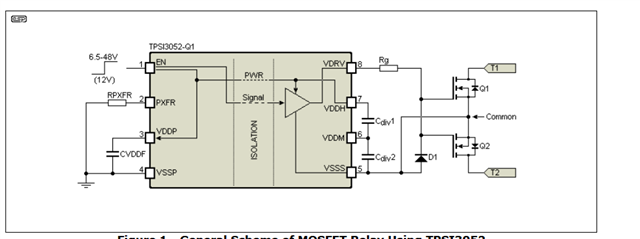

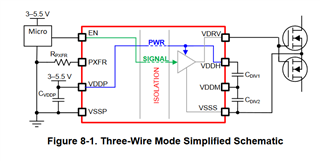

We are planning to design a circuit using the IC TPSI3050.

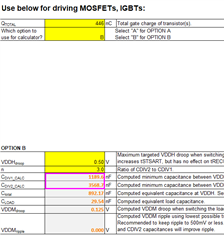

Can you please confirm the use of the pin PXFR.

The datasheet says it controls the power transfer to the VDDH pin.

Please correct me if I am wrong.

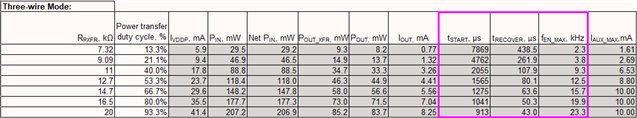

The maximum duty cycle we can obtain is 93%.

Does this mean the VDRV pin will be low during the 7% time of the 25uS?.

The datasheet says "setting EN pin to a logic low causes VDRV to be driven low.".

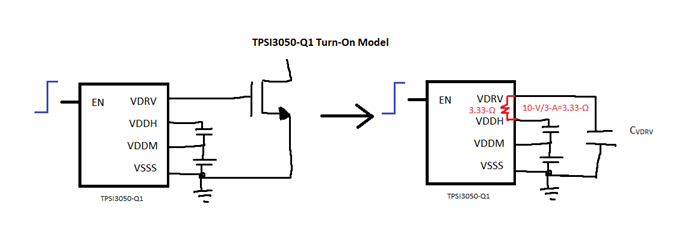

So if we supply the EN pin with a 3.3V (100% ON time), will the VDRV also be 100% time ON?.

If the power transfer is for 93% time, how can the VDRV pin can be 100% time ON?.

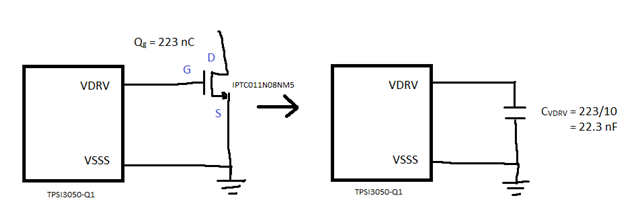

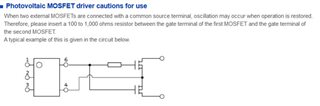

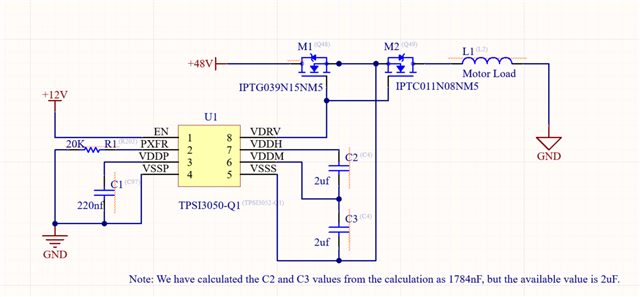

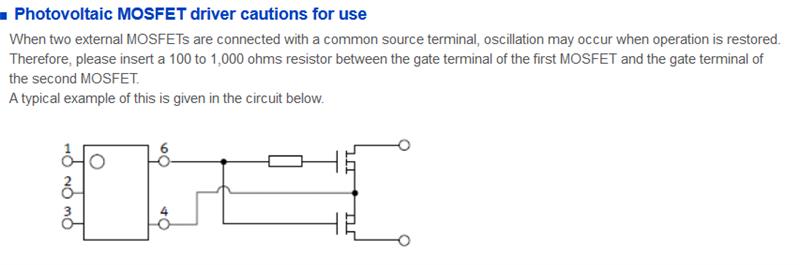

In our application, we need bidirectional current flow. So we are planning to use back to back FET as in the image below.

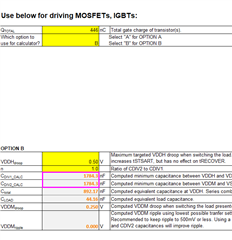

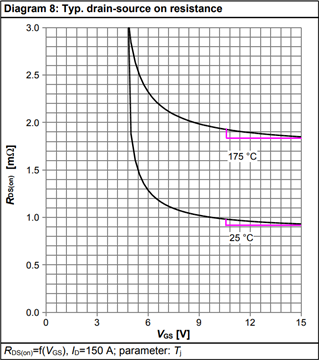

The MOSFET part number is IPTC011N08NM5.

We need 100% ON time for the device.

Looking for your reply