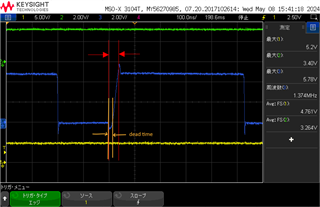

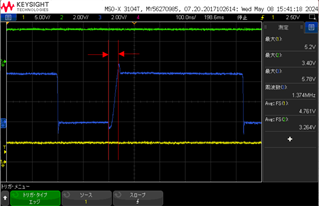

I understood that the dead time when ON is a few ns.

Is it the same time when OFF?

(Are the setting times for ON and OFF different?)

Is the design value 2ns(typ)?

Does the fall time of the waveform and the recovery time of the diode correspond to the dead time?