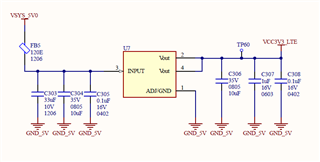

We have an application with LMS1585AIS-3.3/NOPB supplying some of the sensitive circuits. Below is the schematics.

(i) currently we are using ceramic capacitors at both Input & Vout pins. Is any change required for these caps?

(ii) What will be the measured ripple for this IC? We have a requirement for max ripple to be <30mV at 3.3V output. Is any change required to achieve it?

| LMS1585AIS-3.3/NOPB |

Thanks