Hi Team,

Recently when designing the circuit of TPS543B22, I have some questions about EN_UVLO and I would like to ask for advice.

1.

EN_UVLO Pin in Spec Pin voltage Max is 5.5V,

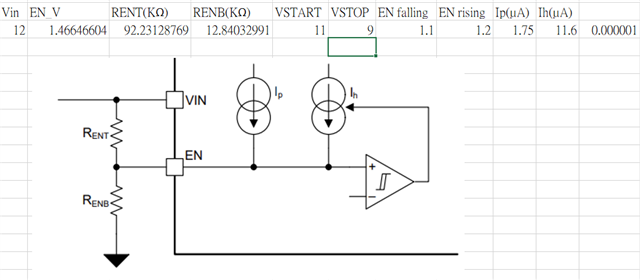

Use WEBENCH® POWER DESIGNER to design. If you design UVLO START: 3.8V, UVLO STOP: 3.4V, the Enable voltage obtained in the 18V system is 5.79V, which seems to exceed the upper limit. Is this correct?

Rent:8.06K,Renb:3.83K

2.

Use WEBENCH® POWER DESIGNER to design.

If you input Min 12V and Max 18V in Vin,

When the EN_UVLO function on the website is turned on, the UVLO_Start display here can be set to a maximum of 12V, Vstart: 12V, Vstop: 10.91V. After calculation by the website, the EN start threshold shows 11.58V.

But isn’t the maximum EN Pin 5.5V? Is this a BUG?

3.

Like Q2, this represents the voltage of the EN Pin. Can it be directly connected to Vin?

EN_UVLO Pin only shows the highest voltage is 5.5V. Is there any protection function inside EN?

If Vin is directly connected to a 12V system, is it feasible without voltage division?

Best regards,

Guanming