Dear TI Team,

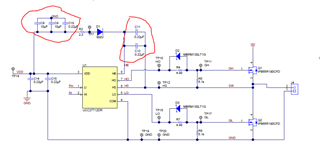

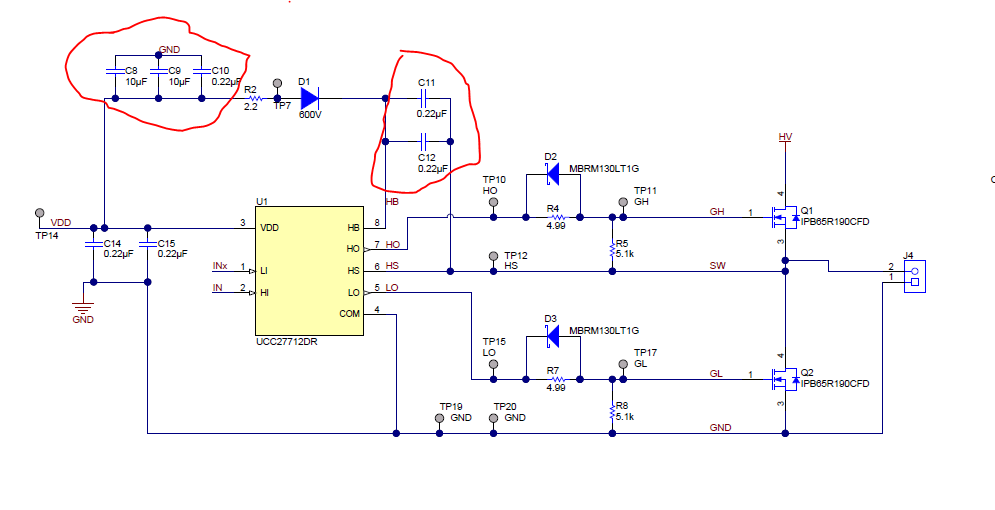

We are facing some issue with UCC27714 driver ( specially at HO & boot caps).

System detail:

Input voltage: 33-34V

Input current :60A

Output voltage: 30V

Output current: 60A( but we are still at 10-15A Only due to this issue)

Switching frequency 230Khz.

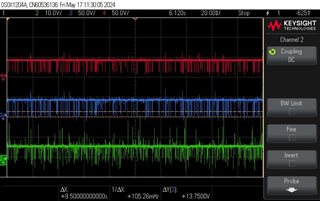

Case 1: Below is the attached waveform of HI_Pin (Green), HO_Pin (Blue) & HB_Pin ( RED) waveforms.

at 10-15A load it seems working fine, As show in below image.

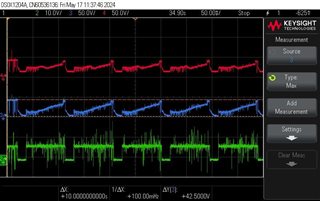

Case2: As we start to increasing load above 15A, then the HO pin waveforms getting corrupted, as shown in below image ( HI_Pin (Green), HO_Pin (Blue) & HB_Pin ( RED) waveforms )

HI ON time ~ 80mSec

HI OFF time ~ 20mSec.

Below is the UCC27714 components details:

1) VDD =12V

2) CVDD=470uF

3) CBOOT = 470nF

4) RBOOT =5R1

5) DBOOT = SS320LWN

6) MOSFET Qg = ~100nC.

7) Rgate = 1R

8) RHI & RLI = 51R

9) CHI & CLI = 220pF

We also tried different CVDD & CBOOT values keeping same DBOOT, RBOOT, VDD etc. But result is the same issue ( Issue still persist)

Case1:

1) CVDD = 1uF

2) CBOOT= 47nF, 100nF & 470nF

Case2:

1) CVDD = 470uF

2) CBOOT= 47nF, 100nF & 470nF

Case3:

1) CVDD = 4.7uF

2) CBOOT= 47nF, 100nF & 470nF

Note: We also monitored the 12V line, it seems constant, there is no change in 12V line nor any fluctuation observed.

-

Ask a related question

What is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.