Other Parts Discussed in Thread: TPS546D24

Hi,

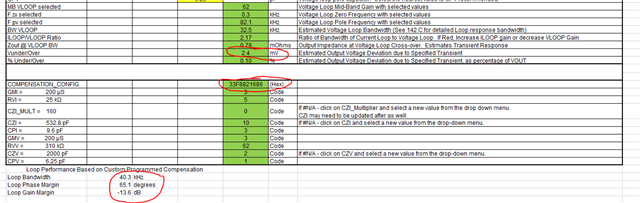

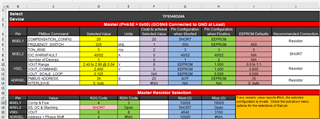

Can you please review my compensation spreadsheet? I'm hoping the loop bandwidth can be improved, and perhaps also phase and gain margin. If I need to adjust the inductor value as well, this is acceptable. I started with a WEBENCH design but I find the compensation calculation to be unreliable (or otherwise not tuned to my particular application).

WBDesign-TPS546D24-12v-2p4v.pdf

12V_MULTI-SLURB01-TPS546x24A_2024-05-17-revA.xlsx

Thanks,

Tom