Hi,

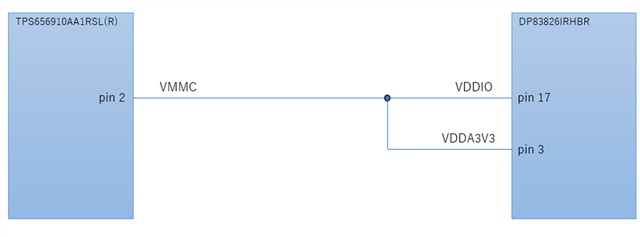

We are using TPS65910AA1RSL(R) as the power supply for DP83826IRHBR.

From the thread below, if the rising voltage of VDDIO is less than 0.5ms, an ESD protection event will occur, It is mentioned that large currents may be consumed.

DP83826I: VDDIO and VDDA3V3 voltage ramp up faster than specified

Q1.

Is there any way to change the VMMC slew rate within the spec (0.5V or more) by the register?

As far as I checked the datasheet of TPS65910, it seems that the slew rate of VCC1,2 can be changed by register.

Q2.

Regarding Q1, if the VMMC slew rate cannot be changed by register, is it appropriate to take measures using peripheral components (RC circuit)?

Thnaks,

Conor