Hi Team,

I think TPS25751 operating in PTCH mode can't let typeC work(sink&source) SO we need to TPS25751 operate in APP mode. Is it correct? (Question#1)

Currently, we don't have EEPROM or EC to configurate the TPS25751 and we try to use micro-controller to send the CMD via I2Ct. We refer to TRM section 5.1. It shows the flow from PTCH mode to APP mode, but it's hard to understand. I find the E2E : https://e2e.ti.com/support/power-management-group/power-management/f/power-management-forum/1345350/tps25751-ptch-mode-update-fails/5131826?tisearch=e2e-sitesearch&keymatch=PTCH%252520OR%252520APP#5131826

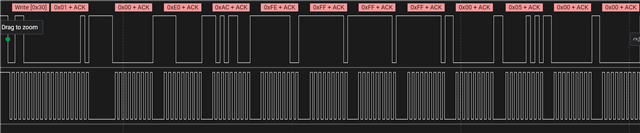

And Kevin shows the saleae log. We want to follow the log and let our TPS25751 enter in APP mode.

1. It reads 3h register and report the 50 54 43 48 (PTCH) OK

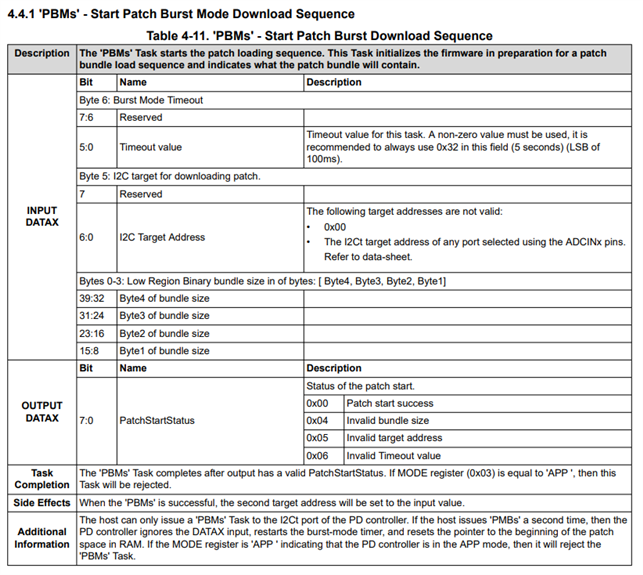

2. It writes 9h(DATA) register, 6bytes, 40 2B 00 00 30 32, what does it mean?(Question#2)

3. It writes 8h(CMD)register, 4bytes, 50 42 4D 73 (Write PBMs) OK

4. It reads 8h(CMD)register, 4byte, and report all "0''. OK

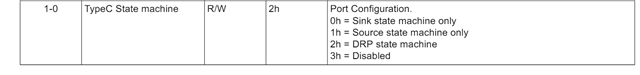

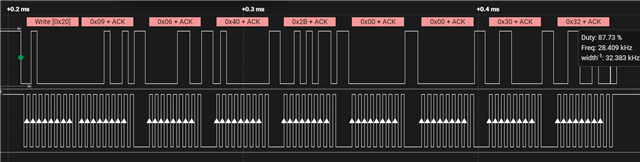

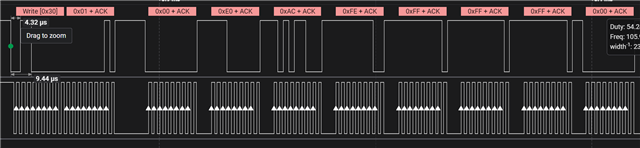

5. it writes 0x30(target address) 1h register so many registers.

How can I define the target address? In datasheet, it said that defined by ADCINx, but in this log, it used 0x20, but why use 0x30 here? (Question#3)

What does the data mean here? (Question#4)

Regards,

Roy