Dear TI experts,

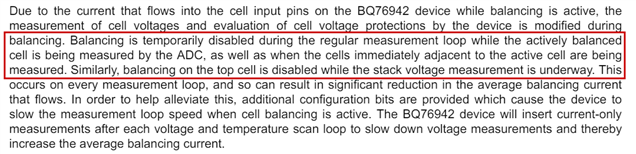

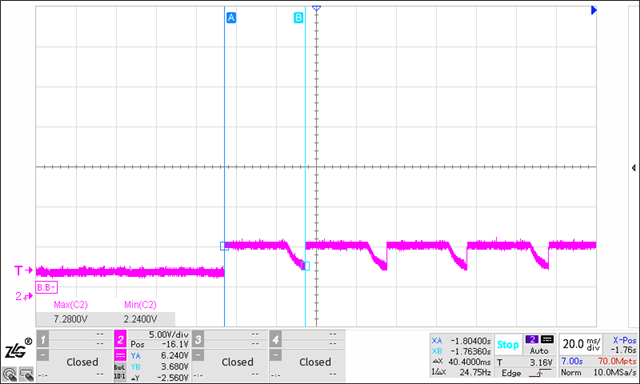

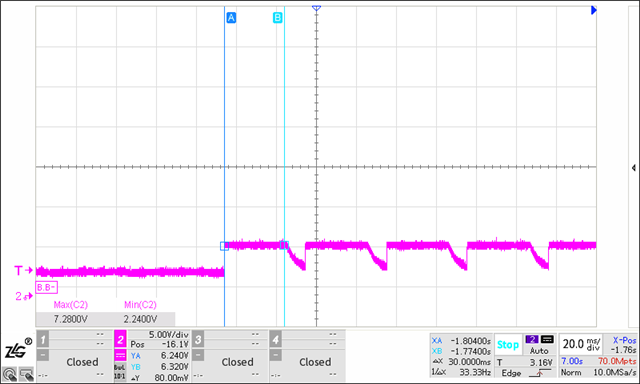

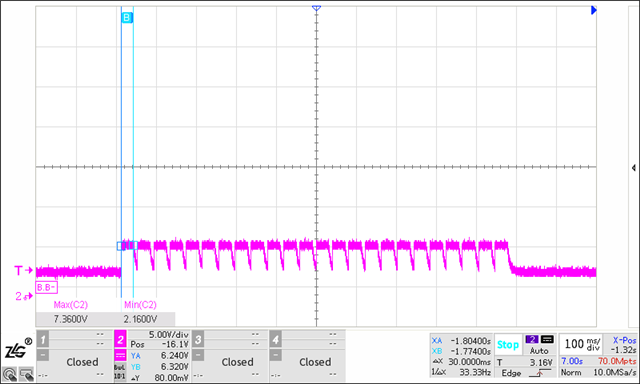

We have used your company's BQ76942 chip, but encountered an issue. During the battery charging process, we found a symmetrical voltage jump between CELL1 and CELL2 displayed on the computer(Figure 1). Subsequently, we captured the voltage of the battery cell using an oscilloscope and found that the period of voltage jump of the battery cell was consistent with that when the battery was balanced(Figure 2-4)

.

.

As far as I know, corresponding cell sampling should not be performed during battery balancing. We want to know the reason for this situation? How to solve it?Looking forward to your reply!