Hi,

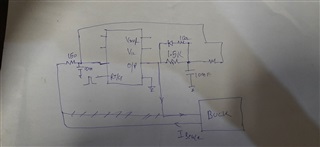

I have designed a synschronous buck converter with uc2843A . I have derived slope compensation ramp from pwm output through RCD circuit to generate a adjustable ramp duty cycle. ramp is add to CS pin. The issue which I am facing is that at higher duty cycles like more that 85% ,there is unstablity. in PWM. So I just wanted to know if there is any maximum duty cycle limitation with peak current mode control. how can I achive stablity at higher dudty cycles?