Tool/software:

Hello everyone,

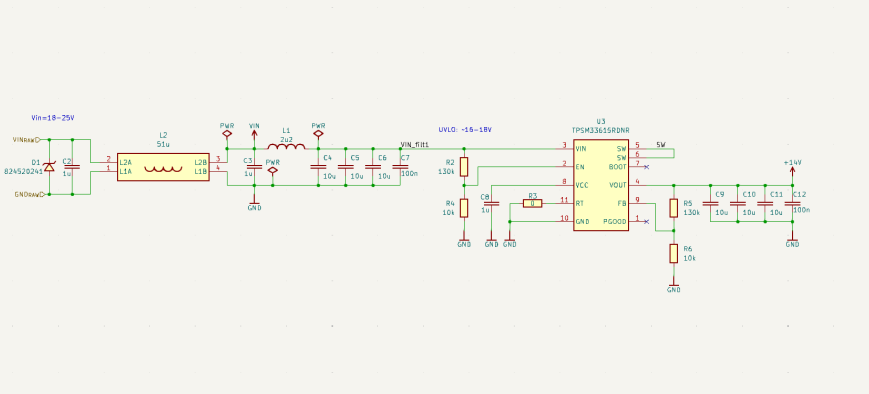

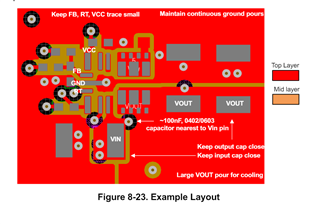

We are currently using the TPSM33615RDNR as a step-down converter from 24 to 14 volts at low load. In our standard circuit, a jumper is provided on the RT pin to ensure that the controller runs at 2.2 MHz, as recommended.

However, this results in approximately 300 mV of ripple with frequencies between 6 and 10 kHz at the input and output, as well as a noticeable coil whine.

We therefore connected the RT pin to VCC for testing, which resolved the issue. The controller now runs at 1 MHz, with a maximum ripple of 30 mV.

However, we have encountered an unexpected outcome. When we allowed RT to float, the controller exhibited the same good behavior. According to the data sheet, however, this is not recommended practice.

Please explain why this is the case and why the behavior does not match the data sheet.

I have never encountered a similar issue with TI.

Best regards,

Fabian