Other Parts Discussed in Thread: EV2400, BQ40Z50, BQSTUDIO

Tool/software:

Dear all,

we have a strange event.

our battery is connected to the application.

upon insertion, the application begins to query over the SMBus line for 18 different commands (such as Voltage 0x09 , Current 0x0a ext.) repeatedly.

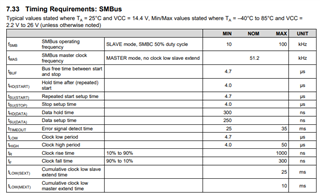

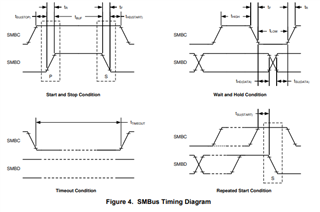

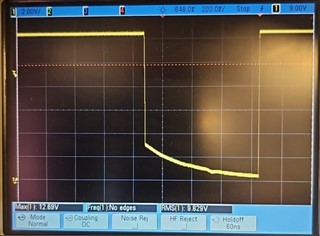

it does so for ~3s then suddenly the communication interrupts, the CLK is distorted and then we have a 25ms when the DATA line is held high then you get the watchdog communication reset.

we recognize the WD reset counter go up after each time.

my questions are:

1) what can cause such CLK or communication interference ? it doesn't happen to a competitor battery with the old bq20z655.

2) we experience a shutdown from the battery ? how can we prevent the battery to shut down at such WD reset event?

the WDF bit is cleared.

tell me further information is needed.

Ran