Tool/software:

Hello,

we have a booster design with the LM5122 and we get some damaged devices after ATP. The feeding supply during ATP provides 20V with a current limit set point of 3A. The fails occured immediately after power-up. The PSU has the following design data:

- Vout = 66V at max. 0.8A (ca. 50W output power)

- Vin = 18-33V (28V typical)

- switching frequency is ca. 210kHz.

- Primary current limit set point ca. 5A via sense resistor (0R015).

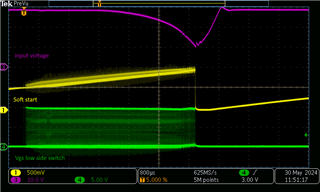

Design works principle ok. However, when supplied with lab supply with current limit set point at 3A so well below the current limit of the DUT (5A) then we have the issue that the PSU cannot normally start since input voltage drops. This behaviour is ok. The issue is that for some units the power components fail (low side switch MOSFET) as well as PWM controller (LM5122).PWM controller failure mode and effects seems to be different. Sometimes there is a short between SW node to AGND. Another effect is the short of VCC pin to ground.

I have measured startup for this scenario (Vin=20V, 3A current limit set point) and seen that sometimes the Low side ON time is quite long, which I don't understand (see screenshots below)

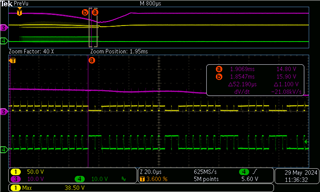

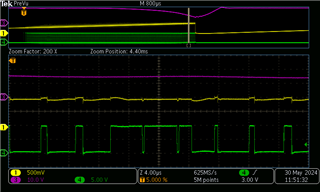

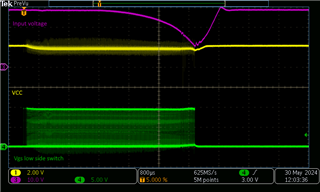

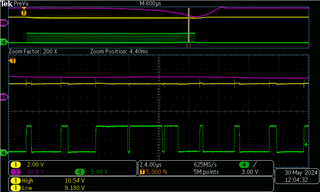

First complete sequence from power-up until first switch if UVLO threshold reached due to too low current limit set point of feeding supply..

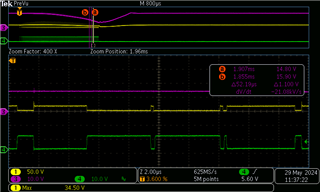

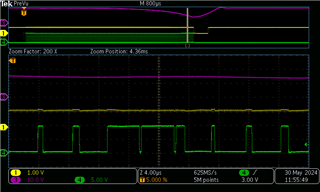

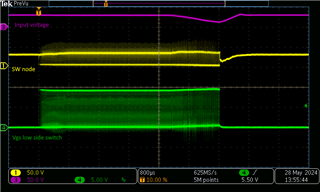

Next figure: the detail for normal switching. It shall be noted that the pulse width increases with time

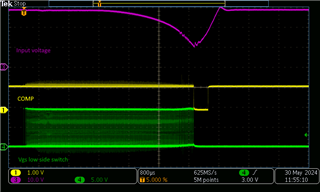

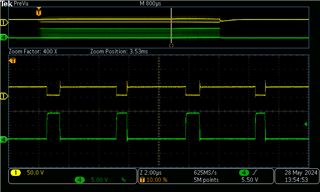

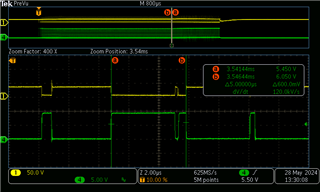

The next figure: detail with unusal long pulse width:

Please note I have switched off channel 3 for the detailed screenshoots (2-3) in order to focus on the most important signals.

First of all the period time is longer than normally, Second there is a short Off-pulse. Input voltage at this zoom area has not dropped. Actually under this scenario I could not catch a damage case. Nevertheless I have the following questions:

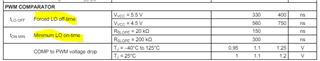

Q1: What are the minimum and maximum pulse width the LM5122 generates during start-up (voltage ramp-up phase)?

Q2: What could cause the unusual long ON pulse shown in last screenshot?

Q3: Is it possible that the LM5122 internal logic / state machine may get stucked and control the Low side MOSFET permanentely ON

For sure, the start-up shall be done with apppropriate current limit of feeding supply. However, I would never expect a device failure (PWM controller itself or one of the switch MOSFETs).

Thanks in advance!

Best Regards Andreas