Tool/software:

Dear IFXer,

We planning design the SiC MOSFET C3M0032120K and UCC5350M in half bridge. and my question is:

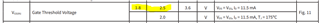

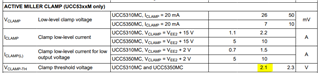

1. I realize the Vth.min of SiC MOSFET is 1.5V and VCLAMP-TH of 5350M is 2.1V. There have any risk when parasitic turn on in half bridge?

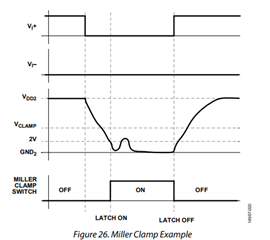

2. if we using the MC function so we can remove negative voltage for turn off, just using the 0V?