Tool/software:

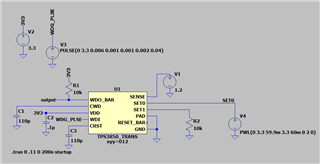

I have a SPICE simulation using the TPS3850, enabling the watchdog partway through operation.

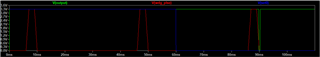

From my understanding after, SET0 is pulled low, as long as WDI has a falling edge within the maximum watchdog time (and continues within the frequency window afterwards) WDO should not be asserted low, but in simulation it's getting asserted low in response to the first WDI edge trigger.

I want to know what the reason behind WDO being asserted low here is as it doesn't match what I'd expect from the datasheet

Thanks!