Tool/software:

Hello,

I would like to ask you about the behavior of UCC28782 when Vsw drops.

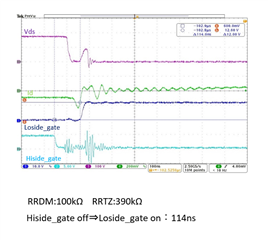

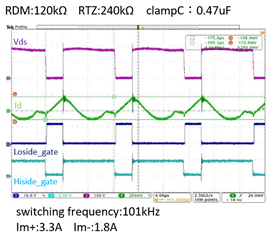

The attached figure shows the waveform when Vsw (Vds) drops.

When the low-side turns on, Vsw rises again. The part circled in red.

I would like to eliminate this part circled in red, is there a way to do this?

I also thought that I could eliminate the part circled in red by extending Tz, so I changed RRTZ from 240kΩ to 390kΩ.

However, Tz did not extend at all. Please let me know if there is a reason why Tz does not change.

Best regards,