Other Parts Discussed in Thread: BQSTUDIO,

Tool/software:

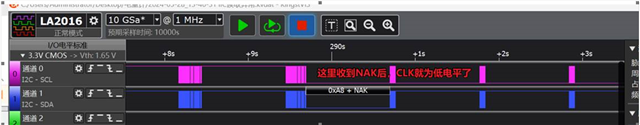

Our test found that the BQ28Z610 coulometer chip could not read the data of the coulometer chip when the terminal read, and the fault was found in the I2C bus. The following is the situation where the I2C bus CLK is low level abnormal after receiving the NACK. Attached is the data file obtained by the logic analyzer. To open the file, please download the software: Qingdao Kingster Electronics Co., LTD. (qdkingst.com) LA2016 Logic analyzer.--The attachment cannot be uploaded to you due to format problems. Could you please provide an email address so that I can send it to you?

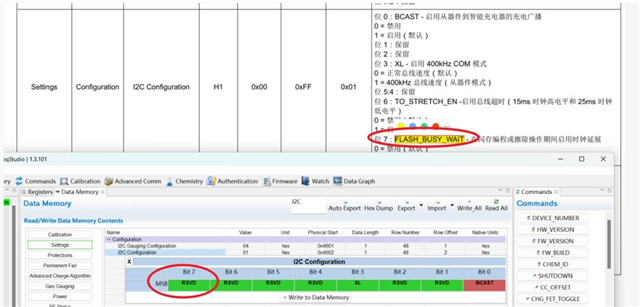

To check IIC exceptions, set Settings->Configuration->I2C Configuration 7 Flash_busy_wait to 1 (the default value is 0).

However, using the BQ host computer (version 1.3.101), we can see that this Bit7 is RSVD, which is inconsistent with the TRM manual that says there is Flash_busy_wait.

May I ask if we can directly set Bit7 to 1 to solve the problem of I2C bus CLK pulling down after NACK? Or is there any other solution?