Tool/software:

Hello,

I would like to ask you a question regarding the burst mode operation of the UCC28782.

(Question 1)

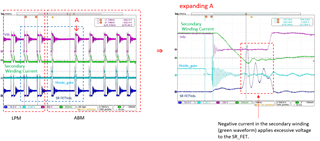

When transitioning from LPM to ABM, excessive voltage is applied to the SR_FET Vds.

Please see the enlarged waveform in the figure below.

When transitioning from LPM to ABM, the first wave of PWMH (Hiside_gate) seems to be extended beyond normal operation so as not to put stress on the SR_FET, according to 8.1 Overview in the datasheet.

However, in the operation shown in the figure below, it is not extended, which seems to be the cause of excessive voltage being applied to the SR_FET.

Is the operation shown in the waveform below expected?

(Question 2)

Even though I have set a hysteresis of 100mV or more for ΔBUR (LPM), LPM mode and ABM mode are repeatedly occurring.

I tried increasing the hysteresis of the BUR pin, but there is no improvement.

Is there any reason for this behavior?

When transitioning from LPM to ABM, the Vcst (BUR) threshold rises, so Id (peak current of the low-side FET) for the first wave when ABM starts should also rise, but it has not. It has not risen from the second wave onwards either.

Is this symptom normal?

Best regards,