Other Parts Discussed in Thread: , UCC27201A,

Tool/software:

Hi,

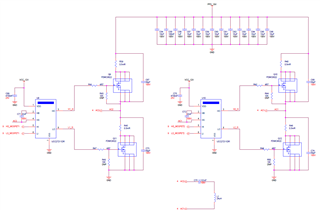

My full bridge inverter using the above mosfet driver and the mosfet used is FDMC8622, during the phase control my gate drive output and the inverter outputs are misbehaving and inverter is not functioning as expected.

This behavior is not seen with low loads less than 100mA during the phase mode. Images are attached for reference.

During the issue case my gate driver U9 output is going to low even my gate driver input is high.

The reference point AC2 is also behaving same as gate driver output. the other end of inverter AC1 doesn't have any issue only at the AC2 end and its high side drive output is having issue.

The inverter is operated at 160Khz phase starts at 135 degree and can go up to 0 degree based on load change or power requirement.