Other Parts Discussed in Thread: LM317, ,

Tool/software:

Good day,

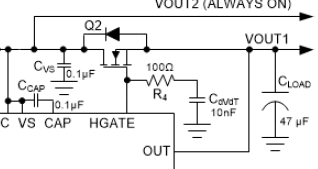

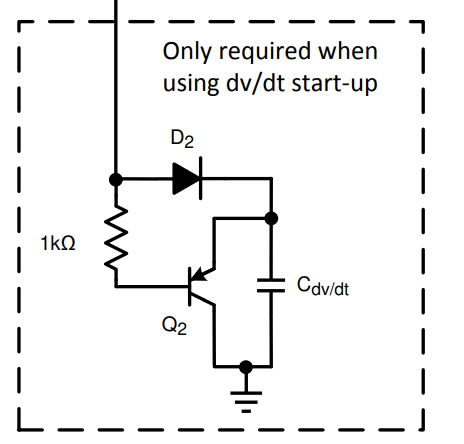

We are experiencing a problem with the way we use the LM74810 power path controller. Please see attached schematic.

VAUX and VBAT are 2 power supply/battery inputs, 24V typical. V_MOTOR is connected to motor driver ICs. Control logic is powered from VAUX.

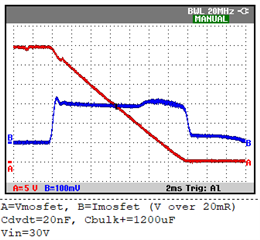

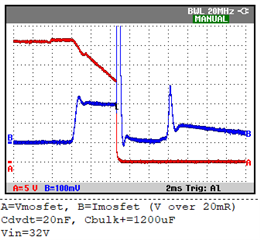

We use LM74910 to choose the power supply for the motor, our choice does not depend on which supply is higher. We choose with VAUX_EN and VBAT_EN (driven by 3V3 processor). In our application VAUX_EN and VBAT_EN are never on at the same time. Switchover time between logic signals VAUX_EN and VBAT_EN is ~20us.

Our experience is that even without high currents in the system (motors always off), Q2 or Q7 fails short. We measure the MOSFET body diode drop, then we switch between VAUX and VBAT several times, and some time later Q2 or Q7 measures 0V/short for the body diode.

Do you have any insight into what we might be doing wrong?

Kind regards