Other Parts Discussed in Thread: LMR14030,

Tool/software:

Dears,

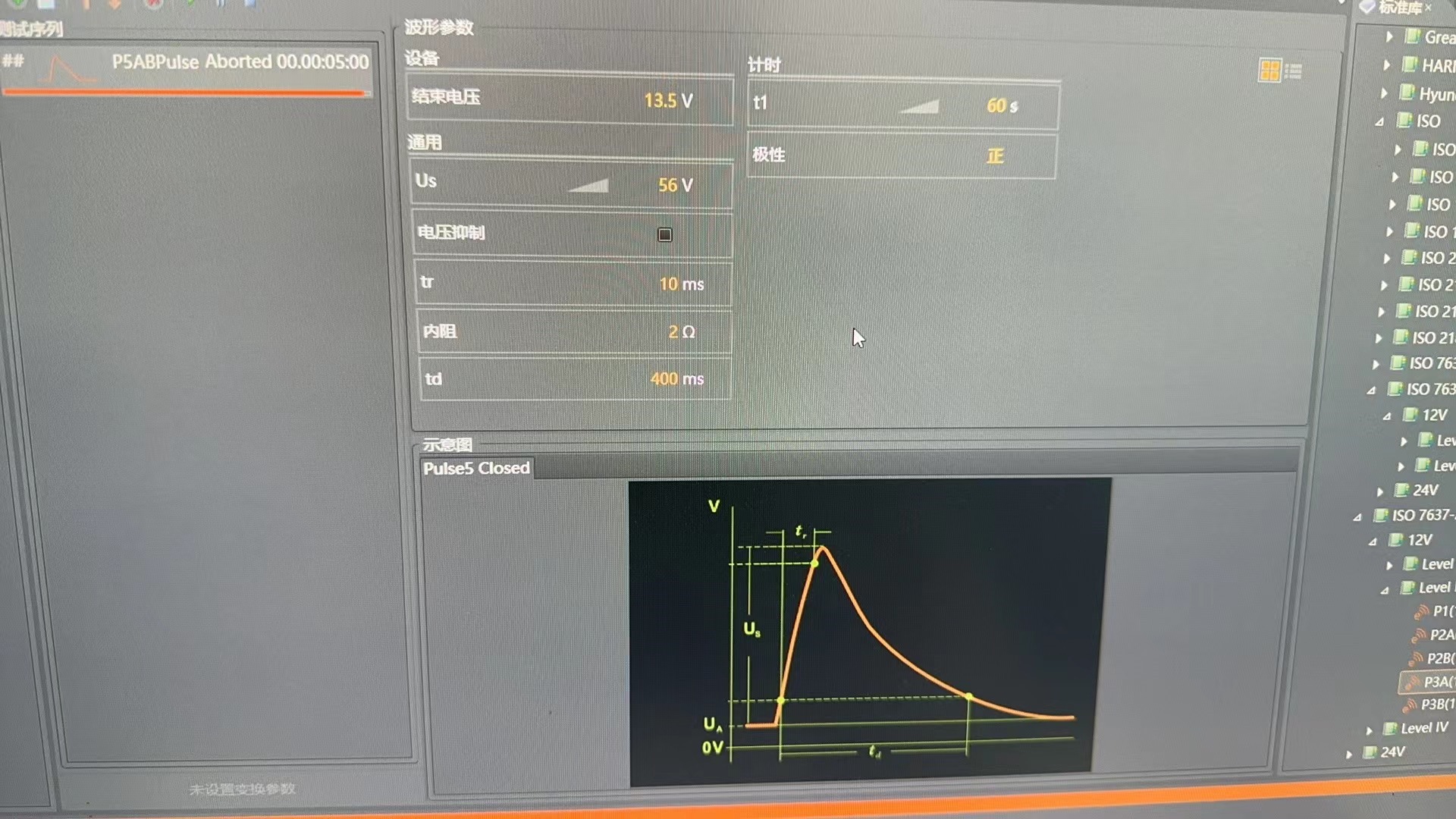

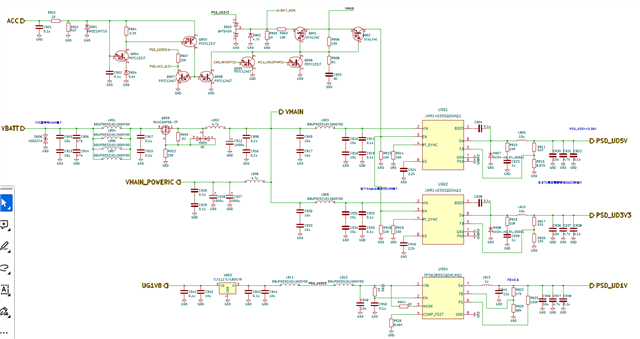

At present, during testing by end customers, it has been found that the VIN pin of LMR14030 is broken and short circuited to ground. The specific cause has not been found yet; The following diagram shows the design principle of our LMR14030-Q1. The entire power tree is fed with VBATT 9-16V and outputs 5.5V/3.3V/1.8V/1V respectively;

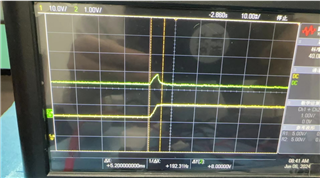

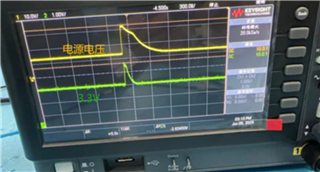

At present, we would like to inquire about the possible cause of damage to LMR14030-Q1. Is it a problem with the schematic diagram, and are there any suggestions for improvement? Currently, we have also found some significant fluctuations in the output voltage of the chip during the Pulse 5b test. Is this normal imagination?

Looking forward to your reply, thank you~