Other Parts Discussed in Thread: TPS65988, TPS65987, TPS65987D

Tool/software:

Hi

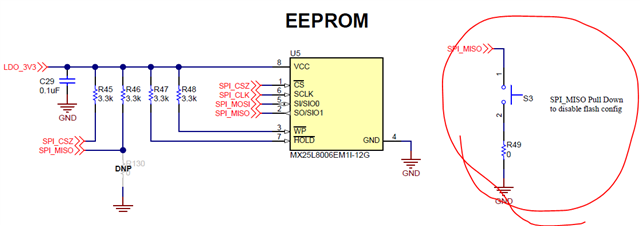

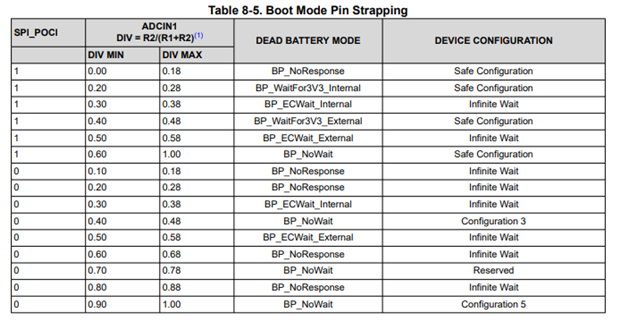

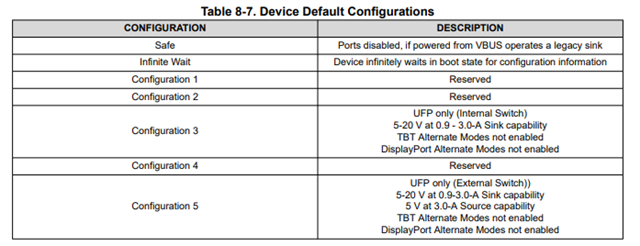

I'm designing a USB PD application board with TPS65987DDK.

Is it possible to program FW into an empty flash via I2C2 of TPS65987DDK from external CPU?

I referred to the document "TPS65987 and TPS65988 SPI Flash Firmware Update Over I2C", but I'm facing 0x2D PatchHeaderErr and cannot proceed next steps.