Tool/software:

Hello,

I have two questions regard the device

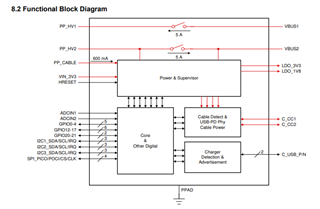

1. What are the D+/D- used for in the device? In the first page of datasheet they are connected while as far as I know, Power delivery messages are transferred only through the CC lines.

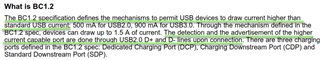

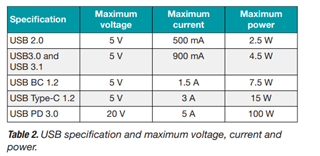

It then written that they support BC1.2 - what is it ? Why D+/D- shall be connected to that device ?

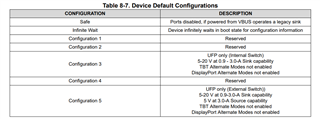

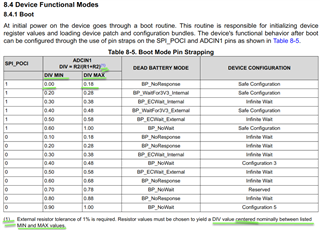

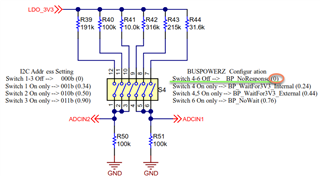

2. How does the device turns up ? Shall it be connected through one of its I2C or SPI to an EEPROM where its SW is loaded from when power up ? Or shall it be connected through one of these interfaces to an MCU ?

Thanks,

Ohad