Tool/software:

hi expert

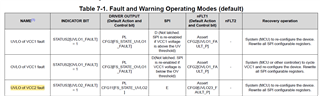

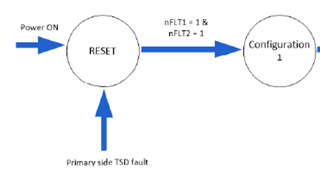

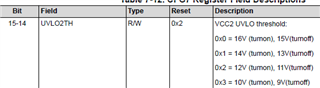

taking UVLO of VCC2 fault as an example, assuming a situation(VCC2 UVLO fault is masked, don't report to NFLT1 ). at the beginning of power up, VCC2 is ok and normal, during UCC5871 working, VCC2 UVLO is trigger. As we know,STATUS3[UVLO2_FAULT] is asserted to 1, BUT driver output is NO action(becasue VCC2 UVLO is masked).

my question is that if VCC2 recovery from abnormal to normal, does UCC5871 can work normally again? can STATUS3[UVLO2_FAULT] be set to 0? or designer need to re-configurate 5871 again?