Other Parts Discussed in Thread: TPS4811-Q1

Tool/software:

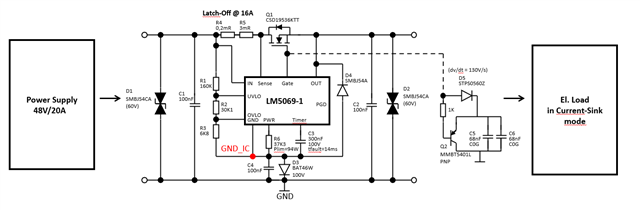

Hello, i have to following test design with LM5069 as an E-Fuse to limit/break currents higher than approx. 16A for 48V nets.

In my Test-Setup i'm using an industrial 48V Power Supply with 20A and short term overload capability (50A) on the input and an electronic load in current-sink mode on the output.

Purpose of the test is to see at which current the IC switches off.

Short summary of the Problem: When the Load-Current is set to 16A, the IC latches off successfully. But when the Load-Current is increased to 18A, the IC does not stay latched off but resets itself.

This problem only occurs with an el. Load on the output, tests with hot short circuits or low resistances were successful.

Notes about the Design / Setup:

- dv/dt is quite slow as high output capacitances up to 10-20mF need to be driven. Tests with Cout=12mF were successful.

- Reverse polarity protection is included with D3 for the IC. Back-to-Back FET is not included as the devices intended to be attached to the output already block reverse currents by themselves.

- D4 was added to prevent negative voltage spikes between OUT and GND_IC

- All measurements shown below are using GND_IC as reference level, not GND.

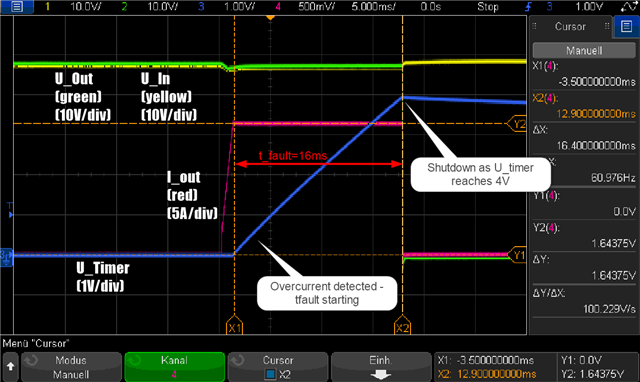

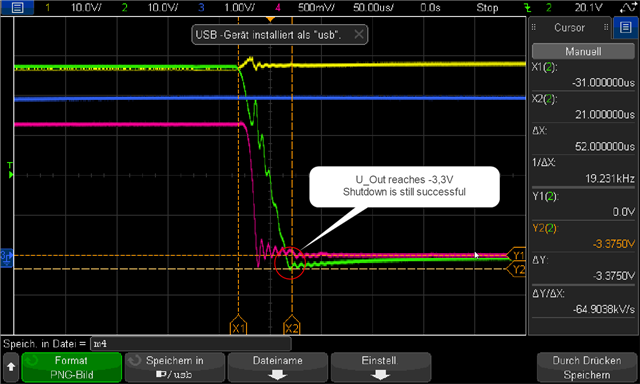

1. Successful test (as reference) - Switching off 16A - Power supply is turned on. After the U_Out has reached 48V the el. Load is activated in current-sink mode @ 16A and the circuit swiches off as intended:

| A:Switch-Off succuessful @16A | B:Zoom of Switch-Off |

|

|

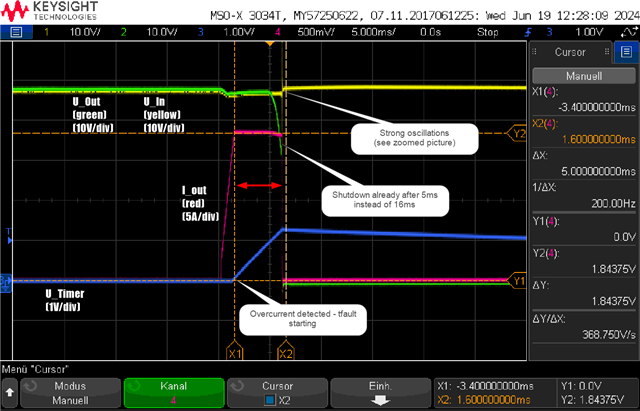

2. Failure - Switching off 18A

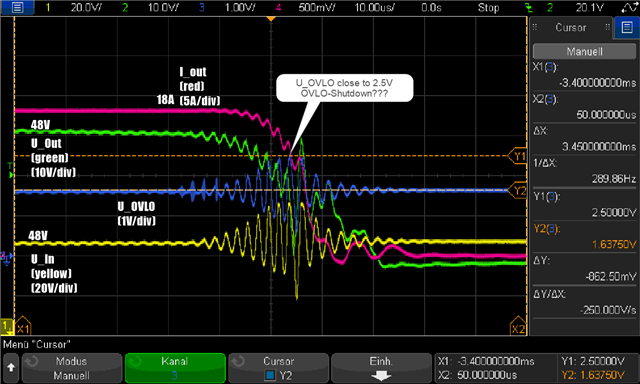

| A: Switch-Off failure @18A | B: Zoom of Switch-Off with U_OVLO (blue) |

|

|

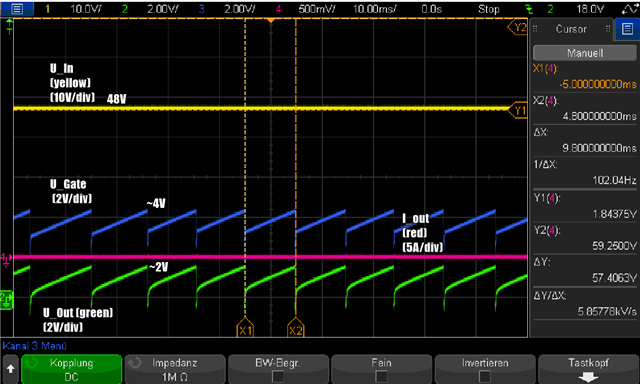

3. After the IC has shut down, there are continous repetitive voltage slopes at U_gate and Uout (while U_timer stays low on 0V). After the el. load is swiched off, the IC seems to restart and goes back into normal operation (Q1 on and Pgd high ohmic) . In my understanding, the IC should be staying latched off.

| A: Voltage slopes after faulty switch-off while el. load is still active (U_timer = constant 0V, not shown on this plot) |

|

My first assumption was that in the second test (failure @ 18A) the device is reset by OVLO as the input touches 2.5V. Still, this doesn't explain the strong oscillations that occur on the input and output line. Apart from that, the 2.5V OVLO-Level is reached while the IC is already swithing off, so this cant be the initial reason for switching off before U_timer has reached 4V.

My second guess was a negative voltage level between OUT and GND(_IC) as this could reset the IC because D4s forward voltage is too high. But if we have a look at picture 1B the IC switches off successful even at voltages of -3.3V. In the failure setup i dont see the OUT voltage going lower than that.

Unfortunately, i dont know the exact impact or behaviour of the el.Load on the test setup but in my opinion the IC is supposed to keep its latch-off functionality no matter what load is attached to it.

Do you have an Idea what could be the reason for this?