Other Parts Discussed in Thread: TL431

Tool/software:

Hello,

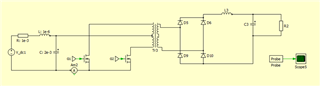

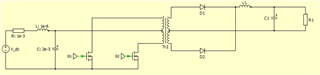

I am using the UC3846DW controller to manage a push-pull converter. The input of the push-pull varies between 18 and 30V, and the output is regulated to 100V. With the knowledge of the input and output voltages and the formula that relates them to the duty cycle, it can be determined that the push-pull operates with a duty cycle between 0.33 and 0.55.

Vout=Vin⋅Duty⋅Transformer RatioV_{out} = V_{in} \cdot \text{Duty} \cdot \text{Transformer Ratio}Vout=Vin⋅Duty⋅Transformer Ratio Transformer Ratio=10\text{Transformer Ratio} = 10Transformer Ratio=10

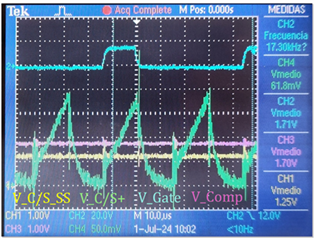

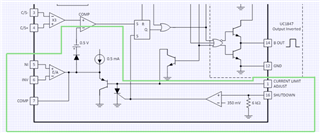

However, in the tests conducted, I have observed that with duty cycles above 0.5, the control starts to fail. Upon analyzing the documentation, I found an application note titled "MODELLING, ANALYSIS AND COMPENSATION OF THE CURRENT-MODE CONVERTER" which indicates that when controlling in current mode with duty cycles above 0.5, a compensator needs to be added.

Do you think it is necessary to add this compensator? And if it is necessary, how could I do it?

Thank you for your assistance!