Tool/software:

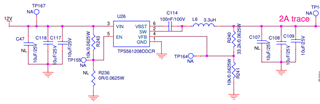

We are using TPS561208DDCR to convert 12 to 3.3V as shown in the schematic below.

In our use case we have noticed that the PMIC behavior of the IC changes under potted condition of the board (The potting material is poured over the entire Board).

3.3 V line with probe in AC coupling.

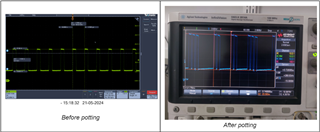

Switching pin waveform before and after potting

Feedback pin waveform before and after potting

Bootstrap pin waveform before and after potting

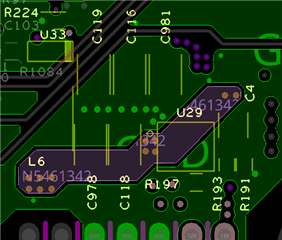

Below is the image of a potted board

This noise is impacting other sensitive ICs on the board. Can someone explain the reasoning behind the change of PMIC behaviour and how to eliminate it?