Other Parts Discussed in Thread: TPS3851

Tool/software:

Hi TI experts

I have a question shown as below.

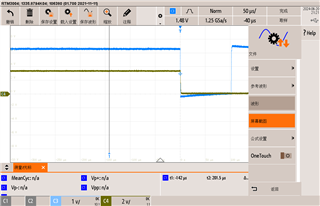

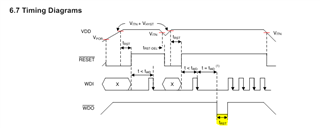

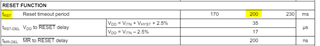

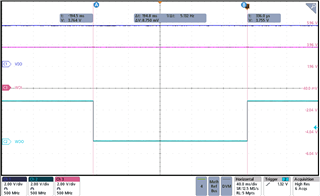

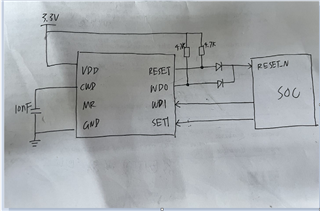

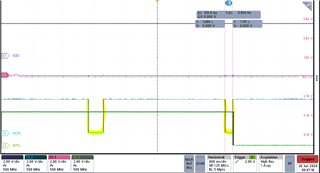

The WDO tRST is only about 100us used in our product as shown in the figure (blue curve), and the WDO pin is connected to our company's SOC. But in another test, the WDO tRST is about 2ms when the WDO pin is connected to an FPGA produced by Xilinx. So I wonder whether the WDO tRST is decided by the load (the SOC system). The typical WDO tRST shown in the datasheet is just the maximum reset timeout period that the chip can support? I do not know whether the WDO tRST is 100us is reasonable because it is different from the datasheet. Thank you!