Tool/software:

Hi team,

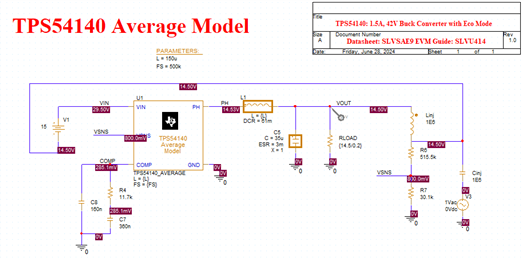

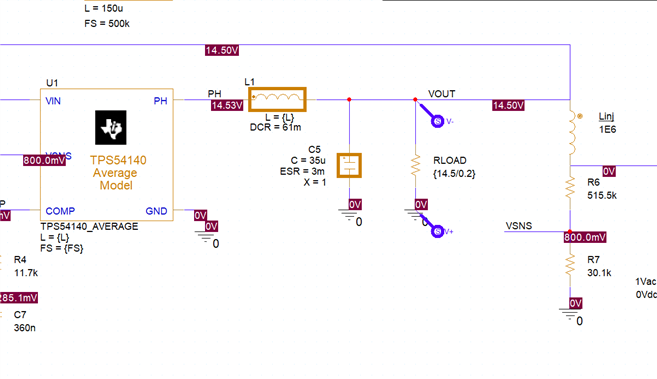

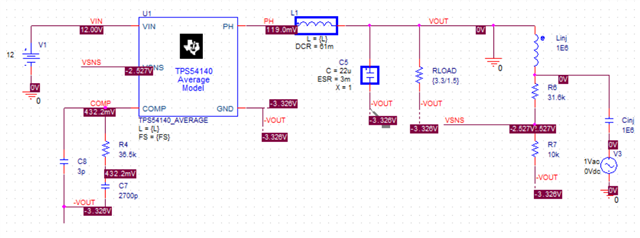

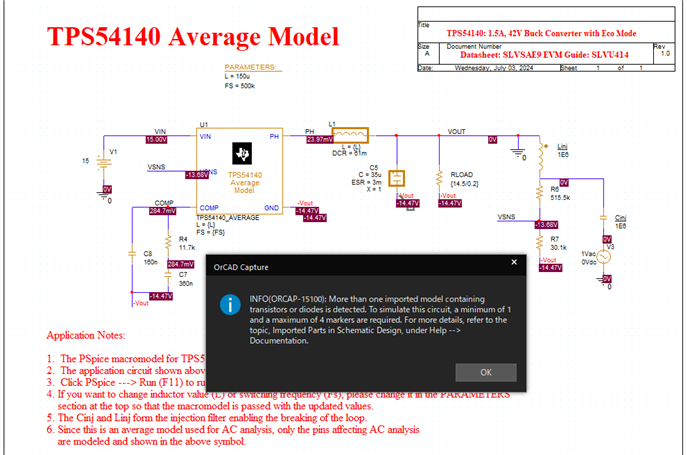

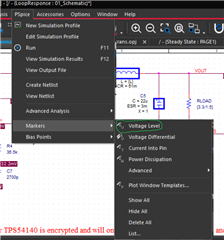

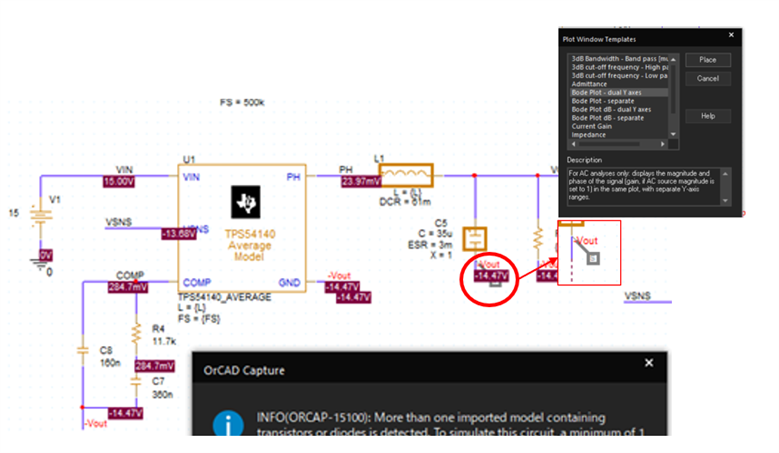

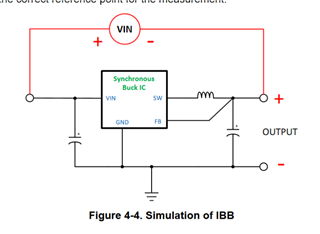

Our customer want to AC analysis by TPS54140 PSpice Average Model to Split-Rail topology.

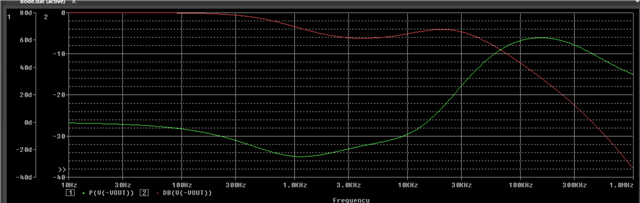

They want to check Bode plot on setting value of result of calculate tools(SWIFTPOSNEG-CALC-v4).

Is it possible by this model?

Or are there other way of AC analysis in the case using this device as Split Rail topology circuit?

Best regards,

teritama