Tool/software:

Hello,

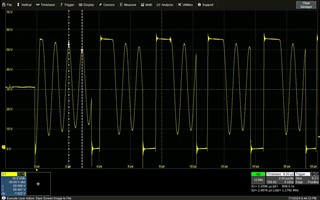

We've configured two LM5122 Synchronous Boost Controllers to work as a master/slave pair, but we're getting a fair amount of subharmonic current oscillations on the power input line. The input voltage range is from 25V to 35V and the output is set for 55V. We should be able to supply about 700W continuous, with brief peaks of up to 2000W. The oscillation amplitude is several amps peak-to-peak, of which the main component is an 18kHz sine wave at lower power levels, or a 96kHz sine wave which starts to dominate at higher power levels. Unfortunately, we are limited to only 80uF of input capacitance and 140uF of output capacitance. We were able to reduce the amplitude of the oscillations by adjusting the slope compensation K factor, and right now we have a value of 1.5 which is giving us the best results so far. The current sense resistors are each 1.5mohms, the undervoltage lockout is currently set to 20V, the Vcc caps are 10uF and the BST caps are 470nF. The boost inductors are each 8.2uH and the PWM switching frequency is set to 300kHz. The feedback compensation network parameters are as follows: Ccomp = 33nF, Rcomp = 10kohm, and Chf = 560pF.

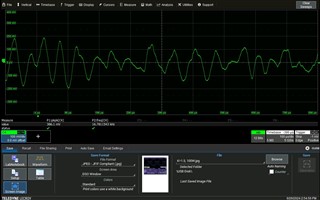

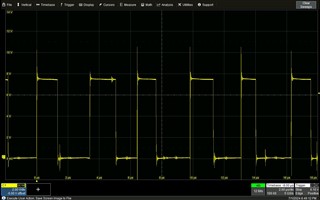

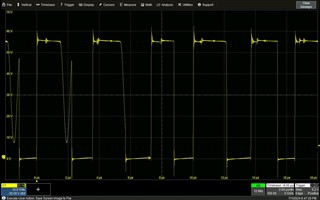

I've attached two scope plots of the input current (AC-coupled, 1A/div) under two different load conditions (100W and 500W).

Another significant problem we're encountering is that the channels are unbalanced, with the master circuit supplying significantly more power that the slave circuit.

Regards,

Florindo