Tool/software:

Dear Designer,

My customer encountered a problem when using Ti's efuse chip TPS259540DSGR, which is described as follows.

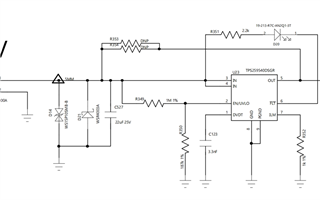

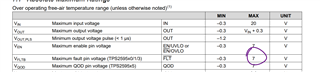

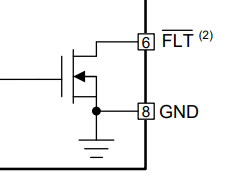

In the figure below, when J2 inputs 13.1V DC, the D20 LED light is on. At this time, the output voltage of TPS259540DSGR is 13.04V, the output function is normal, the Fault pin voltage is 11.51V, and the voltage across the LED light is 1.52V.

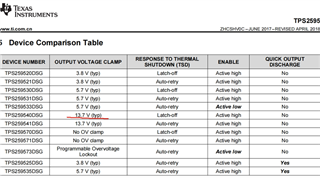

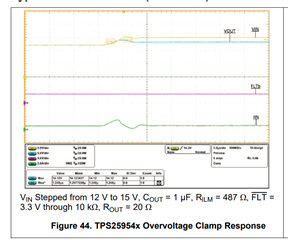

According to the specification, after the input voltage exceeds 13.7V, TPS259540DSGR will start overvoltage protection and clamp the output voltage at 13.7V. But now the input is only 13.1V, why is the LED light on?

Please help analyze the reason, thank you!

Best Regards,

Arabella Zhang