Other Parts Discussed in Thread: TPS650861, , TPS65086

Tool/software:

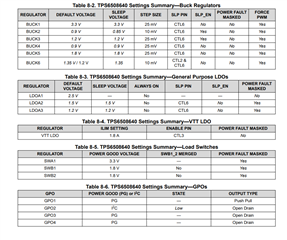

I am designing a power module using the TPS6508640 device. As is true for this family of regulators there are feedback pins that are typically connected to the output of the switching inductor. In another forum item it was asked about how to compensate for drop due to traces to the load. The answer there was that the output inductor should be placed close to the load. However, in my case this is not possible as the design is in a separate module far from the load.

The question is as follows:

Should the feedback be connected to the output of the inductor anyway or should output the feedback pin on the module so that it can be connected to the actual load on the main board?

Many thanks

Michael Stamler