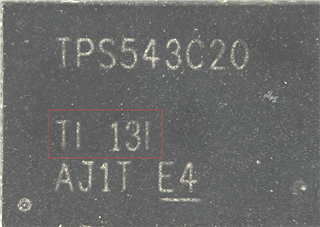

Part Number: TPS543C20

Other Parts Discussed in Thread: TPS543B20

Tool/software:

TPS543C20 failure after 3-6 months of operation, HS_FET and LS_FET burn out and output short-circuit.

Help us analyze the possible causes of the two MOS tubes burning. Application environment:Input:12V,Output:1V, Average current 17A, Peak current 19A.

Below is my schematic design:

SW: