Tool/software:

Dear TI,

We are writing to you today to seek your assistance with an issue we are encountering with our PSU design based on the TPS63070 chip.

Design Overview

Our PSU design utilizes the TPS63070 chip to convert an input voltage from a battery source (ranging from 4V to 6V) to a stable output voltage of 4.8V (load of approximately 3.5W).

EMI Concerns

We have observed that the PSU generates significantly higher levels of radiated emissions when operating in boost mode. To mitigate this EMI issue, we have attempted the following measures:

Adding Snubbers: While not an ideal solution for our battery-powered application, we tried adding snubbers to the design. This resulted in some improvement in radiated emissions in boost mode but had minimal impact near the buck/boost transition point.

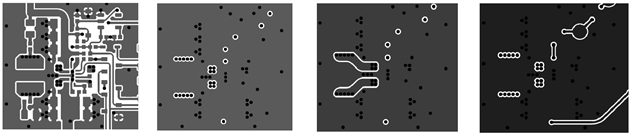

4-Layer PCB: We also transitioned to a 4-layer PCB to improve layout and signal integrity. This again led to some EMI reduction in boost mode but did not address the issue near the buck/boost transition point.

Additionally, we noticed a slight increase in radiated emissions across all input voltages when an electrolytic capacitor (3300uF) was added to the input.

EMI Evaluation

We evaluate the relative level of radiated emissions a using the RSSI value of an ISM band transceiver placed nearby in shielded box.

Request for Assistance

Given the persistent EMI challenges, especially near the buck/boost transition point, we kindly request your assistance in identifying and implementing effective EMI mitigation strategies.

We value your expertise and look forward to your prompt response and guidance in resolving this EMI issue.

Thank you for your time and consideration.

Sincerely,

Maksym