Tool/software:

Hello everyone,

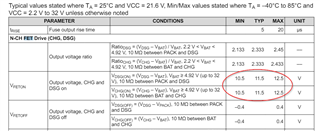

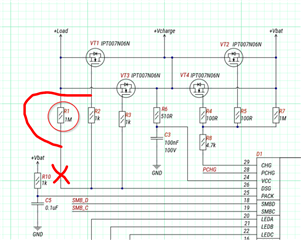

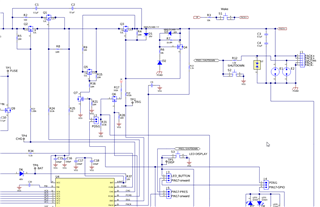

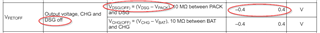

I'm using the bq40z80 chip in my project and I've encountered an issue. When I send the command to turn off the DSG pin, its voltage drops from 27 volts to around 13-14 volts instead of going to zero. As a result, there is always voltage present on the load. What am I doing wrong?