Other Parts Discussed in Thread: TPS25751, TPS25750

Tool/software:

Hello,

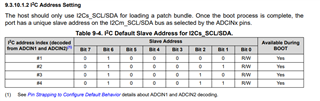

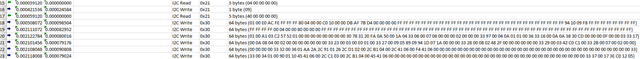

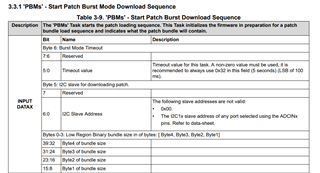

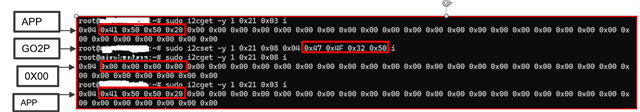

I tried to force the PD to switch to PTCH mode, but I couldn't get it to work properly.

Attached is a photo of the commands I sent. Could you please review them and provide any necessary assistance to help resolve this issue?

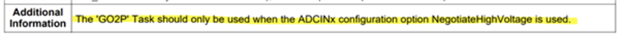

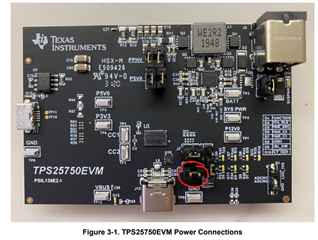

I found this information on the internet, but I'm not sure how to switch to the NegotiateHighVoltage configuration. I am using a TPS25750EVM

Thank you in advance for your assistance. I look forward to your guidance to help me progress with my project.

Best regards,