Other Parts Discussed in Thread: UCC27624

Tool/software:

HI

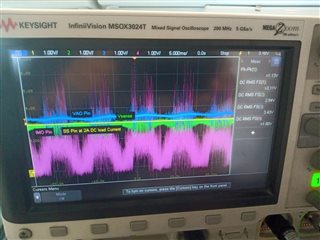

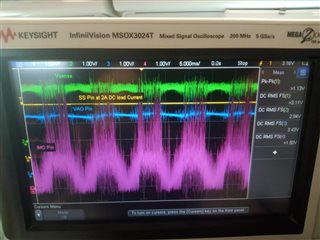

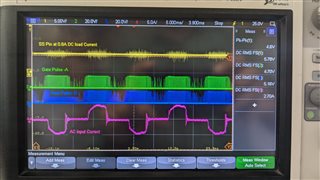

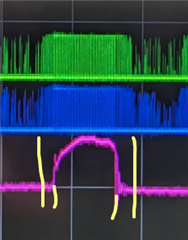

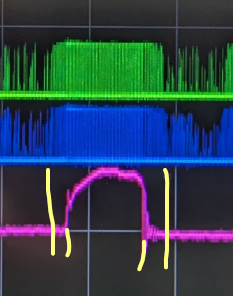

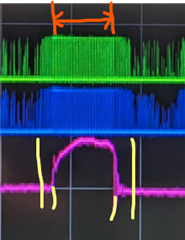

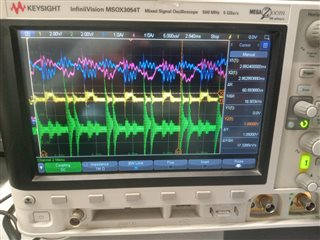

I am Testing a 3.3kw interleaved PFC using UCC28070

Input AC voltage: 230, 50HZ

the output voltage is 400V regulated by IC

But As I am loading the PFC to the current waveform is becoming more of a square type and PF is becoming less. What could be the problem

I can share the schematics in mail ID