Tool/software:

Hi,

I'm designing a product on the PD controller side, I want to use the TPS2376 IC.

The product has two objectives :

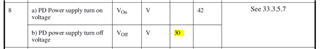

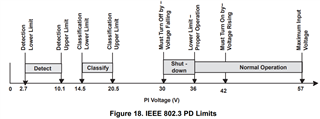

-> it has to be compliant with the 802.3af standard when it will be connected to a device with a PSE.

-> it can also be connected with a device that is not PoE compliant and this device will provide 22.4V through the correct pins of an Ethernet cable.

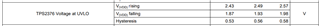

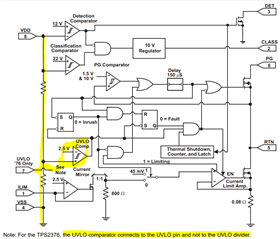

In the datasheet of the TPS2376, there is a sentence saying : "In order to provide flexibility for noncompliant designs, the TPS2376 allows the designer to program the turnon thresholds with a resistor divider. [...] To use the TPS2376, connect a resistor divider between VDD and VSS with the tap connected to the UVLO pin. The total divider resistance appears in parallel with the R(DET), and the combination of the two should equal 24.9 kΩ. The divider ratio should be chosen to obtain 2.5 V at the UVLO pin when V(VDD) is at the desired turnon voltage."

For the non compliant PoE version, the question is : how to choose the correct resistances on the UVLO and the DET pins in order to work with an input voltage at 22.4V ?

For the compliant version, the question is : can we let the UVLO pin floating and put a 24.9kΩ resistance on the DET pin ?

Thank you for your help