Other Parts Discussed in Thread: UCC14141EVM-068

Tool/software:

Dear team,

The customer would like to use UCC14141-Q1 for bias supply.

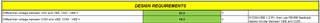

Customer specification is below.

- VDD : 2V, VEE : -18V

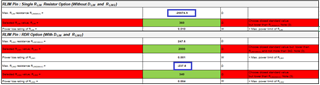

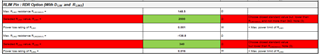

But using calculator, As you can see below, we can see negative Rlim value.

Q1, UCC14141-Q1 can't support customer specification?

Q2, If it can support customer application, Please let me know why Rlim value is negative. How can we fix Rlim2 value?

Please refer to the attached and let me know your opinion.

UCC1414x-Q1_Calculator_V8_LS EMS.xlsx

Thank you.