Tool/software:

Hello,

I am triyng to use TPS65400 for generating 4 indipendent voltages, each one with different regulation; in general Ioutmax = 0.3A and Vout = 7...9V. The control of the Ic is made with I2C protocol.

The schematic is attached as image. GND_POWER and AGND are connected in one point below the IC.

Automatic start-up with external soft start and default sequencing order and timings. All switching frequencies set to defualt with divider 1.

All settings of the TPS are as default excect the one i will mention later.

The problem I am facing is the following: after startup all 4 output voltages are correct with defualt vref (5.6V); when i change the vref value (to 48 decimal) buck 1 and 2 start behaving badly, while buck 3 and work correctly.

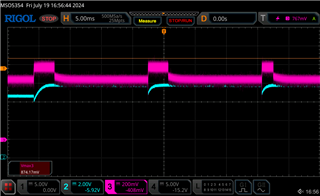

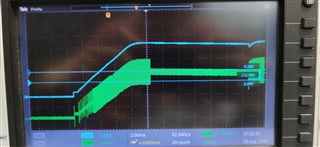

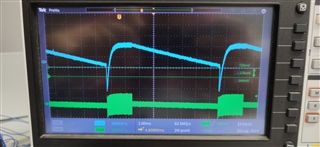

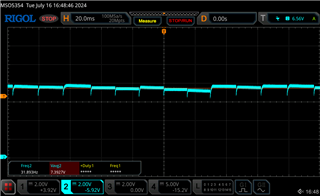

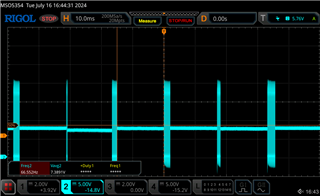

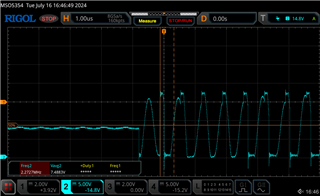

Correct working Vout adìnd Switching:

All this tests are made with no load on the regulators output.

Since i dont need to use buck1 and 2 with output current higher then the other bucks, I tried to set Imax and Gmps to the same values (2.0A max and Isense gain = 5 A/V).

This has made no result.

Next I changed the working frequency, Rosc = 120k so 1.49MHz of switching.

Regulator 3 and 4 still working fine and regulator 1 has improved, regulator 2 same problem as before.

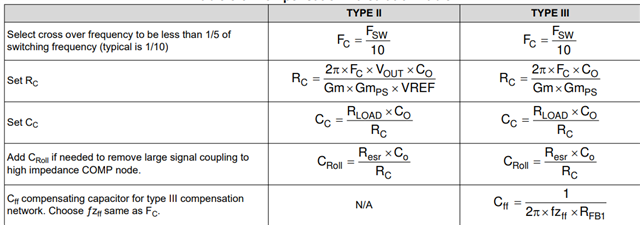

Next i changed the values of R933 = 20k ; C935 = 56nF and C936 = 15p, in order to match the values which work fine with regulator 3 and 4.

Still the problem persists. Is there some other settings i have to use in order to get the 4 bucks to work in the same way?

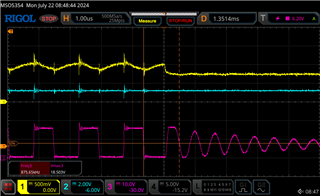

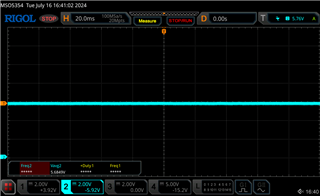

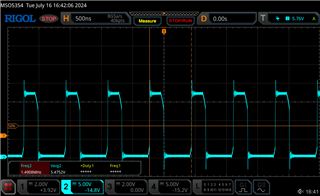

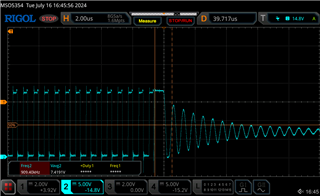

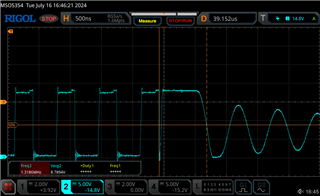

Here the capture of Vout and switching with 48 set as vref in the last test conditions

The Vout seems to be stopping every 20ms, this may be related to Output over corrent, but since there is no load I am not sure.

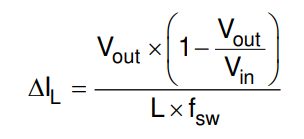

Is there some issue with the setting of the compensation components?

Thank you,

Enrico Bonacini