Tool/software:

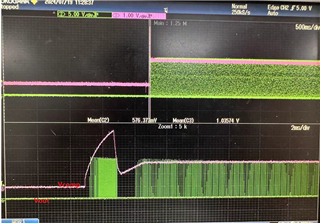

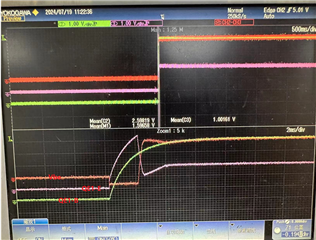

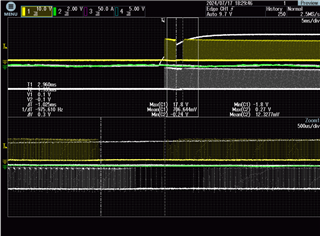

The yellow waveform is the pin6 output waveform, and there is a 0 level of 1ms during the startup process.During the output 0 level time, the level of the 1 pin drops to 0.7V, which may be related to comp

I want to know why is this happening,and whether it will have an impact on the circuit and the use of the chip