Tool/software:

Hi team,

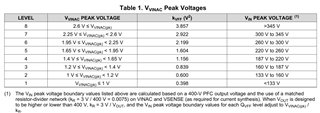

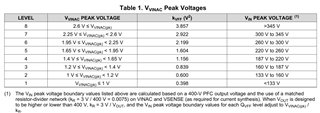

When designing with AC170~264Vin, 750Vout, according to the notes in Table 1, kr = 3V/750V = 0.0004.

If the VIN peak voltage is 240Vpeak (170Vac), Vvinac is 0.096V, so should I use 0.398 for kvff?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Tool/software:

Hi team,

When designing with AC170~264Vin, 750Vout, according to the notes in Table 1, kr = 3V/750V = 0.0004.

If the VIN peak voltage is 240Vpeak (170Vac), Vvinac is 0.096V, so should I use 0.398 for kvff?

Hello Kobayashi-san,

Thank you for your interest in the UCC28070 PFC controller.

Since your design is targeted for high-line-only input range (170~264Vac), I strongly recommend that you use the revised inductor design procedure found in the UCC28070A datasheet, page 35. ( https://www.ti.com/lit/gpn/UCC28070A )

Although the UCC28070 and UCC28070A are nearly identical (except for low switching-frequency range), all of the updates in the recently updated datasheet for UCC28070A also apply to the UCC28070 and UCC28070-Q1. (Those datasheets and the Excel calculation tool have not yet been updated.)

Your calculation is off by a decimal point (kr = 3V/750V = 0.004, so Vvinac for 240Vpk = 0.96V), but your conclusion is basically correct.

kVFF should be taken as 0.398.

However, I have a concern about tolerances which leads to a slight complication with this conclusion.

The VINAC thresholds for the 8 levels shown in Table 1 are valid for rising RMS input voltages. As RMS voltage increases, the line peak voltage progressively crosses the listed thresholds to change kVFF levels.

To avoid "chatter" around a threshold, the thresholds for falling RMS voltages are 95% of the rising thresholds. So the VINAC threshold for crossing from level-2 into level-1 is 0.95V, not 1V. At kr = 0.004, the VINAC peak of 170Vrms is 0.96 which is just above, but very close to, the falling threshold (0.95V) between level-2 and level-1.

Ideally, this means that kVFF for 170Vrms should really be 0.600, since 0.96V will not have crossed below the 0.95V threshold.

My concern is that tolerance for these VINAC threshold is not specified, and there is always some variability from IC to IC and lot to lot. I think the accuracy of these thresholds is fairly tight, but I suggest to allow a 5% margin and presume that the worst-case falling threshold between level-2 and level-1 is 95% of 0.95V = 0.9025V.

You can then force kVFF for 170Vrms to definitely always be 0.398 by using kri = 3/800 = 0.00375 for the input VINAC divider, and still keep kro = 0.004 for the output VSENSE divider. This makes designing for the correct Rimo value more certain.

The side-effect of having different kr values for VSENSE and VINAC is that the current-signal down-slope that is generated by the current synthesizer will be off by about ~6% (750/800 = 0.9375). This is a small error and the calculated value of Rsynth can be adjusted empirically to compensate for the error.

I suggest to optimize Rsynth at the input voltage where maximum THDi is specified; usually this is at 230Vac or 200Vac nominal input voltage.

Regards,

Ulrich