Other Parts Discussed in Thread: LM5156EVM-BST

Tool/software:

Hello team,

If EN and SYNC are used(UVLO is not used), how to connect both EN signal and SYNC signal with this one pin?

Is an additional FET required?

Best Regards,

Austin

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Tool/software:

Hello team,

If EN and SYNC are used(UVLO is not used), how to connect both EN signal and SYNC signal with this one pin?

Is an additional FET required?

Best Regards,

Austin

Hi Moriz,

Thanks for reply.

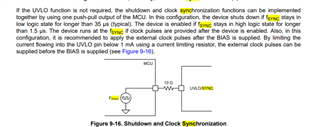

According to datasheet, 1.5us logic high is required for device EN. If the customer uses the circuit like figure 9-16, external sync frequency cannot be greater than 333kHz. Is this correct?

The customer will not use UVLO.

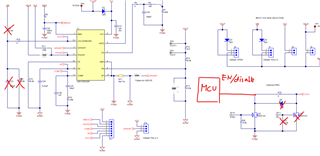

Also, the customer wants to control device on/off by MCU and sync clock by external

If my understanding is correct, can you check below schematic will be okay?

Best Regards,

Austin

Hi Moritz,

Thanks for reply.

Can you confirm the external frequency range?

In the datasheet, "the device is enabled if fSYNC stays in high logic state for longer than 1.5 µs", which means f_sync is limited at 333kHz(1/ (1.5us *2)) or does it mean it stays ENABLE state until disable condition (LOW ~ 35us)?

Best Regards,

Austin

Hi Austin,

or does it mean it stays ENABLE state until disable condition (LOW ~ 35us)?

Yes, this is what it means.

So you can also apply higher switching frequencies than 333kHz.

Best regards

Moritz